国际电子设备会议IEDM 2025 - 台积电TSMC 2NM制程披露

最初的想法

在2024年12月举行的IEDM上,TSMC介绍了:“ 2NM平台技术具有节能纳米片晶体管和与3DIC进行AI,HPC和移动SOC应用程序的互连,”作者是:

Geoffrey Yeap,SS Lin,HL Shang,HC Lin,YC Peng,M.Wang,Pw Wang,PW Wang,CP Lin,Kf Yu,Wy Lee,Hk Chen,Dw Lin,Br Yang,Br Yang,CC Yeh,Ct Chan,Ct Chan,JM Kuo,JM Kuo,CM Ku,CM刘,Th Chiu,Mc Wen,TL Lee,Cy Chang,R.Chen,Ph Huang,CS Hou,YK Lin,YK Lin,FK Yang,J。Wang,S。Fung,Ryan Chen,Chen,Ch Lee,Tl Lee,W。W. ,Dy Lee,Cy Ting,T。Chang,Hc Huang,HJ Lin,C。Tseng,CW Chang,KB Huang,YC Lu,YC Lu,Ch Chen,Co Chui,KW Chen,MH Tsai,Cc Chen,CC Chen,N.Wu,ht Chiang,XM Chen,Sh Sun,Jt Tzeng,K。Wang,YC Peng,HJ Liao,T。Chen,YK Cheng,J.Chang,K.Hsieh,A。Cheng,A。Cheng,G。Liu,A。Chen,A。 ,KC Chiang,CW Tsai,H。Wang,W。Sheu,J。Yeh,YM Chen,Ck Lin,J.Wu,M。Cao,LS Juang,F。Lai,F。Lai,Y.Ku,Sm Jang,Sm Jang,lc lu-杰弗里·叶(Jeffrey Yeap)展示了这项工作。

本文在过去的几年中继续在IEDM而不是技术论文中介绍营销论文。实际上,本文进一步采取了趋势,纸张中没有音调,没有SRAM细胞的大小,并且图形都是没有真实单元的相对性能图。尽管该论文并未提供通常包含在IEDM纸中的技术细节,但它确实描绘了准备2025年生产的过程的图片,并且会议已包装。

在这篇评论中,我们将获取本文中的一些实质细节以及我们自己的分析,并介绍该过程与竞争2NM类流程相比的方式。

就推论的功率,性能和区域(PPA)(PPA)而言,该过程可提供30%的功率提高或15%的性能增益,而> 1.15倍密度与前3NM节点相比。注意:3NM纸参考表明这与N3E相比,而不是N3。

力量

在14nm(Samsung)/16nm(TSMC)节点,三星和TSMC都产生了Apple A9处理器。汤姆(Tom)的硬件测量结果发现,与TSMC相比,三星版的功率性能稍好一些。我们认为A9是为三星首先设计的,因此可以简单地反映出针对三星进行了更优化的设计,该设计已移植到TSMC,但是,两者之间的功率非常接近。从14nm/16nm到达10nm,7nm,5nm,3nm,以及现在的2NM Samsung和TSMC都为每个节点与先前的节点提供了相对功率提高。

在10nm TSMC时,TSMC的功率比三星提供了更大的功率,并一直保持领先地位,直到3nm,三星大门周围(GAA)提供了足够大的改进,以大多数缩小差距到TSMC的3NM FinFET POWER(GAA versus Finfet提供)更大的功率提高)。

TSMC 2NM宣布的功率提高30%对3NM大于三星的25%提高,而TSMC再次保持领先地位。

TechInsights平台上可以免费注册,可以在全文中获得特定的功率因数 在此处的 。

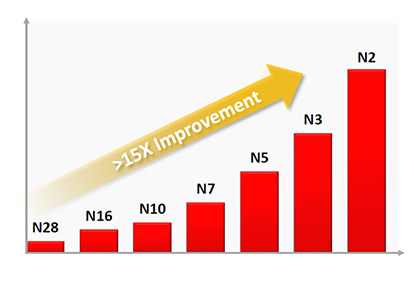

在论文的介绍期间,显示了图表的功率效率和每个瓦与节点的性能。功率效率图是在论文的一个版本中,尽管它不在程序中发表的论文的“最终”版本中。值得庆幸的是,我们捕获了功率效率图,因为分析非常有趣,请参见图1。

图1。TSMC功率效率。

我们拍摄了图像,将其拉到Excel中,并创建了一个Excel图,将其覆盖为28nm bar归一化为1,然后输入其他条的值,直到它们匹配图形为止。如果我们根据TSMC宣布的节点对节点功率改进的节点开始缩放一组杆,

从28nm = 1开始扩展,我们的总改进量小于9倍。从N28到N10的节点很好地匹配,但是图表上的N7的节点显示出比TSMC宣布的更进一的改进。图表上只有N3至N2棒显示了55%的改善,而宣布的30%的改善。

TechInsights平台上免费注册的完整文章中 图2在此处的 。

目前尚不清楚什么可能导致这种差异,但这是一个很大的脱节。这可能就是为什么将图从最后一篇论文中删除的原因。

表现

与上面的功率分析类似,在三星14NM/TSMC 16NM上,Apple A9处理器在这两个过程上具有相同的性能。将这两个过程归一化为1,并将宣布的节点应用于两家公司的节点性能改进,可以比较每个节点的性能。也可以在TSMC 7NM流程上使用Intel 10SF与AMD处理器,以将Intel添加到分析中,并根据Node公告的Intel性能进行计算。

基于此分析,我们相信英特尔18A的2NM类过程的性能最高,而TSMC排名第二,三星排名第三。

TechInsights平台上免费注册的全文中 我们的性能指数值在此处的 。

区域

PPA的第三部分是区域。我们分析了两个“区域”相关因素,一个是高密度逻辑晶体管密度,第二个是SRAM细胞大小。 TechInsights在TSMC N3E过程上进行了详细的逆向工程工作,我们拥有计算标准高密度逻辑晶体管密度所需的所有音高。同样,我们分析了三星SF3E和SF3。本文中的TSMC和公开报表中的三星都为2nm提供了密度改进值。在Intel的情况下,我们在NDA下具有18A的所有音高,尽管我们无法透露可以进行密度比较的特定音高。对于高密度逻辑细胞,TSMC远远领先于三星,而英特尔的密度为第二,英特尔是第二,三星是第三。

可在TechInsights平台上免费注册的全文中 高密度逻辑电池晶体管密度在此处 。

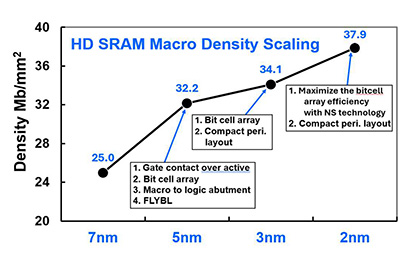

如前所述,TSMC纸不包括SRAM细胞大小,但是有SRAM密度与节点的图表,请参见图3。

图3。SRAM阵列密度与节点。

问题的问题是SRAM阵列不仅包括SRAM单元,而且还包括开销,例如7nm具有25.0 MB/mm 2 ,SRAM细胞在7nm时的大小为0.0270UM 2 。如果您将25.0MB乘以SRAM单元尺寸,则获得0.675mm 2 。 1.000至0.675mm之间的差异 2 是开销,从节点到节点不是恒定的,请参见表1。

可在TechInsights平台上免费注册的全文中 SRAM单元尺寸分析在此处 。

屈服

如今,收益率是一个热门话题,有很多有关三星在3nm处挣扎的报道,并且由于产量较低而失去客户,最近也有一些报道称,英特尔的18A收益率为10%。

在论文中,TSMC报告说,256MB SRAM阵列的平均收益率> 80%,峰值产量> 90%。在这一点上,这些产量表明出色的缺陷密度。在SRAM阵列中测试的成分旁边还有其他产量组件,但这是令人印象深刻的结果。

关于英特尔的10%收益报告,我们有两个独立的可信资源告诉我们,这根本不是真的,收益率要比这要好得多。关于10%收益率报告的其他事项是,又一左右,在开发中有多大的变化,即使这是真的。我们基于资源的信念是报告的10%的收益率是错误的或旧数据。

晶圆价格

广泛散发的另一个数字是,TSMC将以2nm的价格收取每30,000美元的费用。

TechInsights为半导体生产了世界领先的成本和价格模型。在3NM进入生产之前,我们预计每个晶圆<20,000美元,一些客户与我们联系的一些客户坚持认为3nm的价格为20,000至25,000美元。一旦3NM进入生产,我们就可以在TSMC的财务上运行我们的专有法医,并确定我们是正确的,而且数量<20,000美元/晶圆的价格为数千美元。

从3nm Wafers的价格<20,000美元/晶圆的价格到2nm Wafers的30,000美元/晶圆的价格是1.15倍的1.15倍密度提高> 1.5倍,这是晶体管成本的急剧增长,这引起了谁会提高问题的问题。付钱,我们的价格估计<30,000美元/晶圆。还有报道称,通常是TSMC的每个节点的主要客户的苹果公司可能会因为价格而放弃最初的2nm使用,尽管我们还听到了对此的反对。

讨论的另一个要素是,对于TSMC的大量晶圆价格,定价的数量远低于其低容量晶圆价格,因此在任何讨论中都需要考虑数量。总的来说,我们认为30,000美元高于高批量定价的平均值。

如果TSMC价格为2nm晶片的价格为30,000美元/晶圆,他们将为客户提供很大的压力,可以将其转移到Intel和Samsung的2NM级晶圆材料。

背面电源交付

TSMC纸没有解决背面功率交付,但是竞争的2NM流程将实施背面功率交付。

英特尔18A将具有背景电力交付 - 拥有2025 RAMP Intel将是第一个实施这项技术的人。在2026年,三星SF2P流程也将实施背面发电。最后,预计TSMC根本不会在其2NM流程变体上实施背面功率交付,并将等到2027年(最近的报道称这是将其提取到2026年)以在其A16流程上实施。 A16背面电源预计将是一种直接的背面连接,可以提供比英特尔和可能的三星实施更小的轨道高度。

由于英特尔是在这三家公司中最重的性能,因此他们首先实施背面动力交付。

我们听到的有关背面功率交付的另一个有趣的事情是,Foundry HPC客户想要它,但移动客户并不是由于成本而导致的。

对于多个节点,我们可能会看到有或没有背面功率传递的节点,并且鉴于其对金属0的影响,设计规则可能会有所不同。除此之外,我们预计将首先引入VIA,后来从关键互连引入钼。这可能导致节点在HPC的背面功率传递和钼金属化之间分裂,并且没有背面功率和移动的铜金属化。

其他

本文中的最后一个有趣的项目是有关“平坦钝化”的评论。许多过程具有顶部铝制金属层,并且钝化遵循金属轮廓,如果需要诸如杂交粘合的含量,则晶圆表面必须平坦。平坦的钝化大概是平面的顶层,可以粘合。

结论

TSMC已披露了一个2NM流程,可能是可用的2NM班级过程。至少与三星相比,它似乎也是最有效的功率。在绩效方面,我们认为英特尔18a是领导者。早期收益率报告似乎很有希望,但是在我们看来,30,000美元/晶圆价格的报告并不代表该过程的可接受价值,并且可能为英特尔和三星提供了捕获市场份额的机会。 TSMC 2NM应该在今年下半年进行生产。